# VF-T20F256开发板介绍

# CONTENTS 目录

- 01 SZOVS 公司介绍

- 02 易灵思FPGA开发板介绍

- 03 **T20F256 FPGA芯片介绍**

- 04 VF-T20F256 FPGA开发板介绍

- 05 VF-T20F256 Demo资料介绍

- 06 更多产品图片

# O1 PART

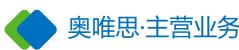

## 深圳市奥唯思科技有限公司

SHENZHEN OVS TECHNOLOGY CO.,LTD.

深圳市深圳奥唯思科技有限公司,简称奥唯思(SZOVS),成立于2021年,坐落于深圳南山。公司核心团队有着数十年的**FPGA图像开发**经验,以及**多媒体ASIC**芯片设计积累。

公司专注于**FPGA图像处理**平台推广、**全国产ISP**相机研制、 **FPGA电子内窥镜系统**开发等,致力于为客户提供快速可量产、高性价比的FPGA图像加速解决方案。

Verilog HDL关键字

奥唯思,为FPGA图像而生......

### 我是作者: FPGA界·韩老师

Coming Soon...

2008年 2012年

2015年

2022年

2024年

2025年

杭州电子科技大学 (本科)

西安电子科技大学(硕士)

中兴微电子技术有限公司 (ZXIC)

深圳市奥唯思科技有限公司 (SZOVS)

### 18年来,从FPGA到图像处理,从逻辑设计到时序约束

- ◆ 入行FPGA 18年,玩转易灵思、高云、Xilinx、Altera、Lattice、紫光、安路、京微雅阁等FPGA

- ◆ 写过近10本FPGA书籍,大部分已经是高校的授课教程,培养FPGA下一代

- ◆ 指导 + 培养过无数FPGA设计、ASIC原型验证工程师

- ◆ 任多个高校 外聘授课教师、企业导师

凭着FPGA行业十几年的技术积累,奥唯思帮客户快速方案落地,为**易灵思、高云、安路、Lattice、图为科技、创龙科技、思特威、成都微光**等知名企业提供FPGA图像解决方案,得到了市场广泛的支持与认可……

奥唯思,为FPGA图像而生……

www.szovs.com

## 奥唯思 & 易灵思 合作关系

奥唯思,为FPGA图像而生.....

凭着FPGA行业十几年的技术积累,以及图像处理ISP的项目经验,奥唯思与易灵思共同进步,从Trion到钛金系列,从FPGA开发板,到工业、医疗图像解决方案,不断创新,不断突破……

● 2023.10: 承接国产FPGA创新设计大赛(易灵思赛道)

● 2024.06: 参加上海 易灵思 & 思特威 视觉大会

● 2024.10: 承接国产FPGA创新设计大赛 (易灵思赛道)

● 2025.04: 参加北京 易灵思 开发者大会

● 2025.08:参加深圳 易灵思 & 思特威 视觉大会

● 2025.09: 参加成都 易灵思FPGA研讨会

● 2025.10:承接国产FPGA创新设计大赛 (易灵思赛道)

● 2025.XX: 独家设计TJ135硬核FPGA开发平台, 推向全球

● 持续前讲...

# 02 PART

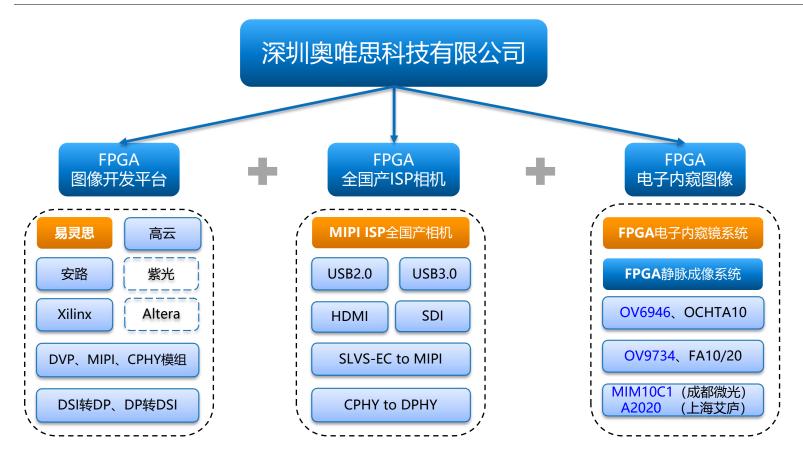

# 易灵思FPGA开发板介绍

## 易灵思FPGA开发板产品

## 易灵思 FPGA开发板

VF-TJ135 高性能硬核图像开发板

VF-Ti60F100 超小低功耗60K模块

VF-Ti60F225 钛金FPGA开发板

VF-T35F324 Trion FPGA开发板

VF-T20F256 Trion入门FPGA开发板

| 型号          | 系列            | 资源   | 存储                 | DVP      | MIPI     | 图像接口                        | 通信接口            | 特性描述                                         |

|-------------|---------------|------|--------------------|----------|----------|-----------------------------|-----------------|----------------------------------------------|

| VF-TJ135    | 钛金<br>16nm    | 135K | LPDDR4<br>EMMC     | /        | √<br>双目  | MIPI 2.5G *2<br>HDMI, LVDS  | UART<br>以太网     | 合封RISC-V 4核 (主频1G)<br>16G 8lane Serdes RX/TX |

| VF-Ti60F100 | 钛金<br>16nm    | 60K  | HyperRAM<br>合封32MB | /        | √<br>双目  | MIPI CSI/DSI<br>HDMI        | UART            | 15*15mm拇指核心板<br>60K合封32M内存MIPI应用             |

| VF-Ti60F225 | 钛金<br>16nm    | 60K  | DDR3               | <b>√</b> | <b>√</b> | HDMI, LVDS,<br>MIPI CSI/DSI | UART<br>USB2.0卡 | 易灵思钛金16nm FPGA<br>低功耗高速MIPI开发                |

| VF-T35F324  | Trion<br>40nm | 35K  | DDR3               | <b>√</b> | √<br>双目  | HDMI,LVDS<br>MIPI CSI       | UART<br>USB2.0卡 | 易灵思钛金40nm FPGA<br>低功耗高速MIPI开发                |

| VF-T20F256  | Trion<br>40nm | 20K  | SDRAM              | <b>√</b> |          | RGB<br>HDMI <del>子卡</del>   | UART<br>USB2.0卡 | 入门级FPGA开发板<br>集成FPGA下载器                      |

备注:按照易灵思产品规格容量排列

# CMOS摄像头模组

| <b>型</b> 号  | 厂家     | 色彩  | 靶面    | 像素     | 分辨率       | 曝光 | 帧率  | 接口        | 镜头  | 焦距     | 特性           |

|-------------|--------|-----|-------|--------|-----------|----|-----|-----------|-----|--------|--------------|

| VS-SC535HGS | 思特威    | 黑白  | 2/3   | 3.45um | 2440*2048 | 全局 | 80  | MIPI DPHY | СП  | 16mm   | 大靶面、高分、全局    |

| VS-SC233HGS | 思特威    | 黑/彩 | 1/2.6 | 3.0um  | 1920*1080 | 全局 | 120 | MIPI DHPY | M12 | 3.6mm  | 全局、高速、1080P  |

| VS-SC130GS  | 思特威    | 黑/彩 | 1/2.7 | 4um    | 1280*1024 | 全局 | 240 | MIPI DHPY | M12 | 3.6mm  | 全局、高速、低照度    |

| VS-SC2210   | 思特威    | 彩色  | 1/1.8 | 4um    | 1920*1080 | 卷帘 | 60  | MIPI DPHY | M12 | 6mm    | 大靶面、低照度      |

| VS-SC101IOT | 思特威    | 彩色  | 1/4.2 | 2.9um  | 1280*720  | 卷帘 | 30  | DVP 8bit  | M12 | 4mm    | 彩色、集成ISP     |

| VS-IMX586   | 索尼     | 彩色  | 1/2   | 0.8um  | 8000*6000 | 卷帘 | 30  | MIPI CPHY | /   | 3.95mm | 4800万,CPHY相机 |

| VS-AR0135   | Aptina | 黑白  | 1/3   | 3.75um | 1280*1024 | 全局 | 60  | DVP 8bit  | M12 | 3.6mm  | 全局黑白、车规      |

| VS-MT9V034  | Micron | 黑白  | 1/3   | 6um    | 752*480   | 全局 | 60  | DVP 8bit  | M12 | 4mm    | 全局、850nm敏感   |

| VS-OV5640   | 豪威     | 彩色  | 1/4   | 1.4um  | 2592*1944 | 卷帘 | 15  | DVP 8bit  | M12 | 4mm    | 彩色,集成ISP     |

| VS-MT9M001  | Micron | 彩色  | 1/2   | 5.2um  | 1280*1024 | 卷帘 | 30  | DVP 8bit  | M12 | 8mm    | 大靶面、低成本      |

备注:提供基于易灵思FPGA的驱动Demo

# O3 PART

# T20F256 FPGA芯片介绍

## T20F256硬件资源

| 特点                                  | T4       | Т8    | T13          | T20          | T35          | T55          | T85          | T120         |

|-------------------------------------|----------|-------|--------------|--------------|--------------|--------------|--------------|--------------|

| 逻辑单元 (LEs)                          | 3,888    | 7,384 | 12,828       | 19,728       | 31,680       | 54,195       | 84,096       | 112,128      |

| 掩模可编程存储(MPM)                        | <b>✓</b> | ~     | ~            | ✓            | _            | _            | _            | -            |

| 嵌入式 RAM 位 (kb)                      | 77       | 123   | 727          | 1,044        | 1,475        | 2,765        | 4,055        | 5,407        |

| 18x18 乘法器                           | 4        | 8     | 24           | 36           | 120          | 150          | 240          | 320          |

| 锁相环 (PLLs)                          | 1        | 5     | 5            | 7            | 7            | 8            | 8            | 8            |

| 最大 GPIO (1)                         | 55       | 97    | 195          | 230          | 230          | 278          | 278          | 278          |

| LVDS (TX, RX)                       | -        | 6, 6  | 13, 13       | 20, 26       | 20, 26       | 52,52        | 52, 52       | 52, 52       |

| DDR3, LPDDR3, LPDDR2<br>(1066 Mbps) | -        | -     | -            | 16           | x16          | x32          | x32          | x32          |

| 内置 CSI-2 控制器的<br>MIPI 4Lane DPHY    | 1-       | _     | 2 RX<br>2 TX | 2 RX<br>2 TX | 2 RX<br>2 TX | 3 RX<br>3 TX | 3 RX<br>3 TX | 3 RX<br>3 TX |

#### T20F256 无DDR3/MIPI IP, T20F324才有

#### 表 1: T20 FPGA Resources

| LEs <sup>(2)</sup> | Global Clock<br>Networks | Global Control<br>Networks | Memory (kbits) | Embedded<br>Memory<br>Blocks (5 Kbits) | Embedded<br>Multipliers |

|--------------------|--------------------------|----------------------------|----------------|----------------------------------------|-------------------------|

| 19.728             | Up to 16                 | Up to 16                   | 1044.48        | 204                                    | 36                      |

#### **Features**

- High-density, low-power Quantum® architecture

- Built on SMIC 40 nm process

- Core leakage current as low as 6.8 mA<sup>(1)</sup>

- FPGA interface blocks

- GPIO

- PLL

- LVDS 800 Mbps per lane with up to 20 TX pairs and 26 RX pairs

- MIPI DPHY with CSI-2 controller hard IP, 1.5 Gbps per lane

- DDR3, LPDDR3, LPDDR2 x16 PHY with memory controller hard IP, up to 1066 Mbps

- Programmable high-performance I/O

- Supports 1.8, 2.5, and 3.3 V single-ended I/O standards and interfaces

- Flexible on-chip clocking

- 16 low-skew global clock signals can be driven from off-chip external clock signals or PLL synthesized clock signals

- PLL support

- Flexible device configuration

- Standard SPI interface (active, passive, and daisy chain)

- JTAG interface

- Optional Mask Programmable Memory (MPM) capability

- · Fully supported by the Efinity® software, an RTL-to-bitstream compiler

#### 表 1: T20 FPGA Resources

| LEs <sup>(2)</sup> | Global Clock<br>Networks | Global Control<br>Networks | Embedded<br>Memory (kbits) | Embedded<br>Memory<br>Blocks (5 Kbits) | Embedded<br>Multipliers |

|--------------------|--------------------------|----------------------------|----------------------------|----------------------------------------|-------------------------|

| 19.728             | Up to 16                 | Up to 16                   | 1044.48                    | 204                                    | 36                      |

# O<sub>4</sub> PART

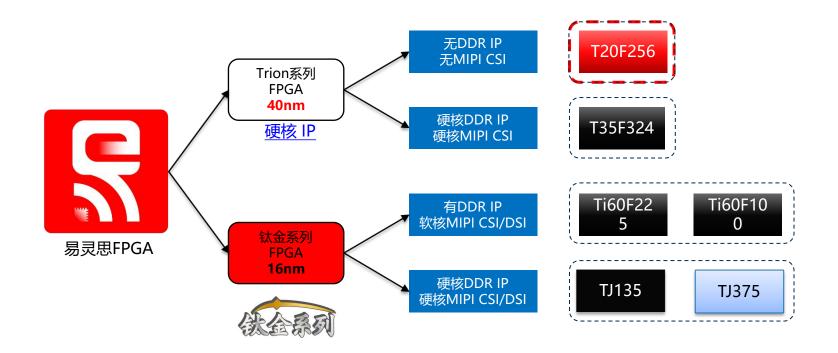

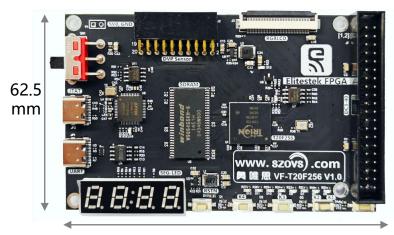

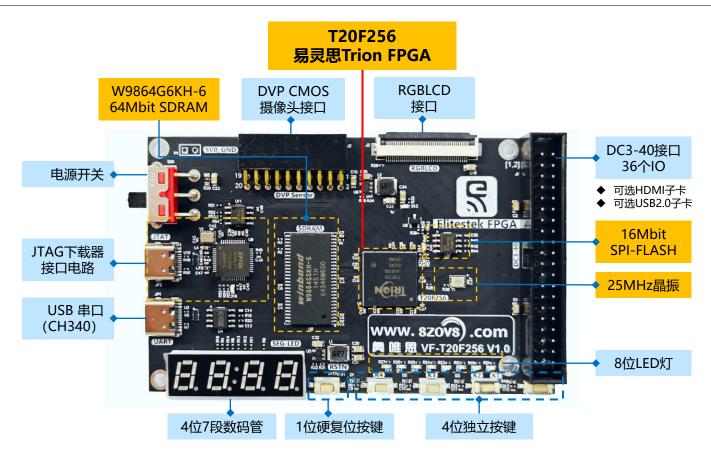

# VF-T20F256 开发板介绍

## VF-T20F256 开发板参描述

100mm

| 参数     | 描述                                                                                                                                                                                                                        |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 供应商    | 奥唯思 科技                                                                                                                                                                                                                    |

| 核心板型号  | VF-T20F256开发板                                                                                                                                                                                                             |

| FPGA厂家 | 易灵思(国产FPGA)系列                                                                                                                                                                                                             |

| FPGA型号 | T20F256                                                                                                                                                                                                                   |

| FPGA资源 | <ul><li>20K 逻辑单元,集成SDRAM IP, 36个DSP</li><li>1044 kbits, 5 PLLs</li></ul>                                                                                                                                                  |

| PCB工艺  | 4层 1.6mm 沉金 黑色/绿色                                                                                                                                                                                                         |

| 板载芯片   | <ul><li>1个25MHz有源晶振</li><li>1个16Mbit SPI-FLASH</li><li>1个64Mbit SDARM (W9864G6KH-6)</li></ul>                                                                                                                             |

| 板载外设   | <ul> <li>1个TypeC USB串口</li> <li>8个LED测试灯</li> <li>1个硬复位附件,4个FPGA独立按键</li> <li>1个4位7段数码管</li> <li>1个DVP CMOS摄像头接口</li> <li>1个RGB LCD屏FPC接口(5.5寸800*480、7寸12024*600)</li> <li>1个DC3-40用户接口(36 IO,可扩USB2.0、HDMI等)</li> </ul> |

| JTAG接口 | 板载TypeC接口的易灵思FPGA下载器                                                                                                                                                                                                      |

| 供电     | USB TypeC供电                                                                                                                                                                                                               |

## VF-T20F256 DC3-40接口定义

|        |           |    | JT |    |           |       |

|--------|-----------|----|----|----|-----------|-------|

|        |           |    |    |    |           |       |

| _      | DC3-40-0  | 1  |    | 2  | DC3-40-1  |       |

| _      | DC3-40-2  | 3  |    | 4  | DC3-40-3  | _     |

|        | DC3-40-4  | 5  |    | 6  | DC3-40-5  | _     |

| _      | DC3-40-6  | 7  |    | 8  | DC3-40-7  |       |

|        | DC3-40-8  | 9  |    | 10 | DC3-40-9  |       |

| DEVOL  |           | 11 |    | 12 |           | Шh.   |

| D5V0 - | DC3-40-10 | 13 |    | 14 | DC3-40-11 | יון 🗀 |

|        | DC3-40-12 | 15 |    | 16 | DC3-40-13 |       |

|        | DC3-40-14 | 17 |    | 18 | DC3-40-15 |       |

|        | DC3-40-16 | 19 |    | 20 | DC3-40-17 |       |

|        | DC3-40-18 | 21 |    | 22 | DC3-40-19 |       |

|        | DC3-40-20 | 23 |    | 24 | DC3-40-21 | _     |

|        | DC3-40-22 | 25 |    | 26 | DC3-40-23 |       |

|        | DC3-40-24 | 27 |    | 28 | DC3-40-25 |       |

| D3V3   |           | 29 |    | 30 |           | Шh.   |

| ם אסרם | DC3-40-26 | 31 |    | 32 | DC3-40-27 | . իր  |

|        | DC3-40-28 | 33 |    | 34 | DC3-40-29 | _     |

|        | DC3-40-30 | 35 |    | 36 | DC3-40-31 |       |

|        | DC3-40-32 | 37 |    | 38 | DC3-40-33 |       |

|        | DC3-40-34 | 39 |    | 40 | DC3-40-35 | _     |

|        |           |    |    |    |           |       |

DC3-40

定义 DC3-40编号 定义 GPIOL 42 GPIOL-24 CLKO D<sub>0</sub> 2 D1 GPIOL 35 CTRL7 D2 D3 GPIOL-27 CLK3 4 GPIOL 43 GPIOL 28 CLK4 D4 5 6 D5 GPIOL 55 D6 8 D7 GPIOL 47 GPIOL 49 D8 9 10 D9 GPIOL 67 D5V0 11 12 **GND** GPIOL 54 D11 D10 13 14 GPIOL 60 GPIOL 56 D12 15 16 D13 GPIOL 72 GPIOL 70 CBSEL0 GPIOR 76 PLLINO D14 17 18 D15 GPIOL 73 D16 19 20 D17 GPIOL 68 GPIOR 87 D18 21 D19 GPIOR 86 GPIOR 85 D20 24 D21 GPIOR 99 23 GPIOR 89 D22 25 26 D23 GPIOL 66 **GPIOL 71 STATUS** D25 GPIOR 78 D24 27 28 D3V3 29 30 GND GPIOR 80 D27 D26 31 32 GPIOR 79 GPIOR 82 D28 D29 GPIOR 84 33 34 GPIOR 83 D30 35 36 D31 GPIOR 93 GPIOR 95 D32 D33 GPIOR 97 37 38 GPIOR 90 D34 39 40 D35 GPIOR 92

# 05 PART

# FPGA开发板 Demo资料介绍

## FPGA开发板 配套Demo介绍

| 序号  | 工程名                      | 设计描述                                         |

|-----|--------------------------|----------------------------------------------|

| 0   | 00_T20F256_FLASH_Loader  | VF_T20F256 SPI-FLASH桥接工程(仅固化用bit)            |

| 1   | 01_LED_8bit_Addr_Test    | 板载8bit LED自加工程                               |

| 2   | 02_LED_8bit_Water_Test   | 板载8bit LED流水灯工程                              |

| 3   | 03_KEY_4bit_Test         | 板载4bit按键测试工程                                 |

| 4   | 04_SEG_4bit_Test         | 板载4bit数码管测试工程                                |

| 5   | 05_UART_115200_Test      | 板载UART串口115200波特率测试工程                        |

| , 6 | 06_RGBLCD_800480_Test    | 800*480 RGBLCD驱动工程                           |

| 7   | 07_SDRAM_LCD_800480_Test | 基于SDRAM读写的800*480 LCD显示工程                    |

| 8   | 08_MT9M001_800480_Test   | 基于MT9M001摄像头的实时显示系统(1280*1024 crop到800*480)  |

| 9   | 09_OV5640_800480_Test    | 基于OV5640摄像头的实时采集显示系统(800*480)                |

| 10  | 10_MT9V034_800480_Test   | 基于MT9V034摄像头的实时采集显示系统(752*480填充显示于800*480)   |

| 11  | 11_AR0135_800480_Test    | 基于AR0135摄像头的实时采集显示系统(1280* 720 crop到800*480) |

| 12  | 12_SC1336_800480_Test    | 基于SC1336摄像头的实时采集显示系统(1280*720 crop到800*480)  |

◆同时根据采购选型,亦可提供基于7寸1024\*600 LCD的工程,以及基于配套HDMI子卡的工程

## FPGA开发板 套餐介绍

可选

VF-T20F256 FPGA开发板

800\*480 RGB IPS触摸屏

可选

ADV7513 HDMI输出子卡

无需下载器, 板载集成!

USB2.0 68013通信子卡

# 06 PART

更多图片展示

## VF-T20F256 开发板测试场景

#### DVP CMOS模组,支持

- 130万彩色MT9M001

- 500万彩色OV5640

- 30万黑白MT9V034

- 130万黑白AR0135

- 130万彩色SC1336

VF-T20F256 易灵思FPGA 开发板

- 5.5寸800\*480 RGBLCD

- 7寸1024\*600 RGBLCD

● 最高支持1080P60

- USB2.0子卡

- 提供PC Demo

# 奥唯思,为FPGA图像而生...

# **THANKS**

官方网站: www.szovs.com (资料下载)

官方淘宝: https://szovs.taobao.com

"奥唯思FPGA"店铺

FPGA论坛: <u>www.crazyfpga.com</u>

FPGA交流群: 851598171 (QQ)

♀ 深圳市南山区朗山路11号同方科兴科学园E栋501

CrazyFPGA 公众号

深圳奥唯思 官微

企微业务 联系方式